SOI-MEMS devices microfabrication

- Boyu Zhang

- Jul 25, 2023

- 2 min read

Micro-fabrication is a state-of-the-art technology that enables the design and manufacture of miniature devices with incredible precision. Our research group, named the N3L group, is devoted to exploring Nanomaterials, Nanomechanics, and Nanodevices (the three N's). Under the Nanomechanics domain, our primary aim is to characterize and understand crucial microstructural, mechanical, electro-mechanical, chemo-mechanical, and thermo-mechanical properties of nanomaterials and nanostructures. To facilitate these studies, we have developed the push-to-pull (PTP) device, along with a sophisticated micro-fabrication process.

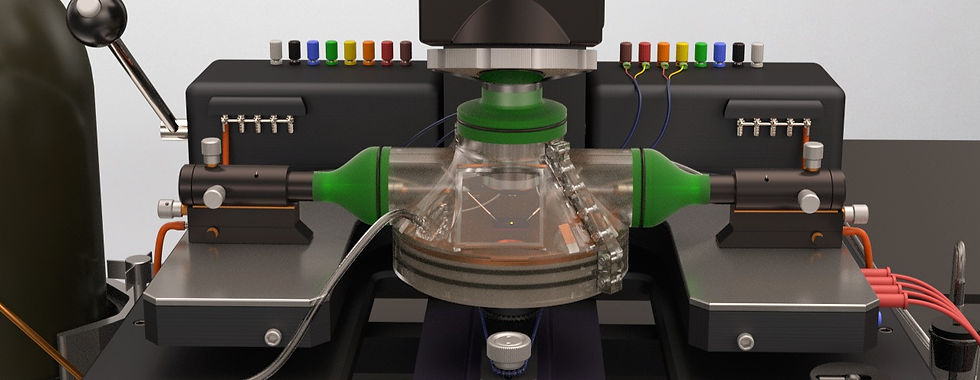

The PTP device was ingeniously designed to integrate with an in-situ SEM/TEM indentation system, allowing us to conduct various mechanical tests, such as tensile, fracture toughness, fatigue, and creep tests, on both 1D materials (fibers and nanowires) and 2D materials (graphene, h-BN, TMD, COF, MXenes, etc.). The well-designed microstructure of the PTP device efficiently converts the indent force from the indentation process into uniaxial tensile force, which is then applied to the samples. Over the past two decades, we have continuously updated our design to expand our testing capabilities. Presently, we can test a wide range of existing 1D and 2D materials, even under extreme conditions, such as high temperature and high strain rates.

Unlike other tests, mechanical studies are strongly dependent on the sample, demanding a large number of tests to yield reliable results. The use of commercial devices (costing over $200/device) can be a significant burden for ordinary laboratories. To address this challenge, we have developed a robust micro-fabrication protocol for batch fabrication of PTP devices, achieving high-yield production. Leveraging the facilities of the university cleanroom, we can now fabricate more than 2000 devices per week.

Our manufacturing process for push-to-pull MEMS devices begins with specialized Silicon-On-Insulator (SOI) wafers. These wafers consist of a thin layer of silicon dioxide sandwiched between a silicon substrate and the top silicon device layer. This unique structure enables the creation of movable microstructures and allows the addition of electrical components while minimizing electrical interference and leakage currents. We are currently working on designing our next-generation MEMS devices, which will enable mechanical-electrical coupled tests, extreme-high temperature tests, and liquid cell tests.

Overall, our dedication to micro-fabrication and the development of the push-to-pull device has opened up exciting possibilities for exploring the mechanical properties of nanomaterials and nanostructures, making significant strides in the world of nanotechnology and beyond.

Comments